GAME & MEDIA TECHNOLOGY (MSC PROJECTS)

Cache Simulator

Real-time cache simulator with visualizations.

Overview

In this project, I created a cache simulator that simulates the behavior of a computer's cache system. The task that is being performed is filling the pixels of a fractal image. I have implemented different caches, such as the fully associative cache, direct mapped cache, N-way set associative cache, and a hierarchy of L1-L2-L3 N-way set associative caches. The caches support read/write functions, and these functions are used to read/write data for the fractal being drawn (reading a single byte and writing a single byte).

Showcase

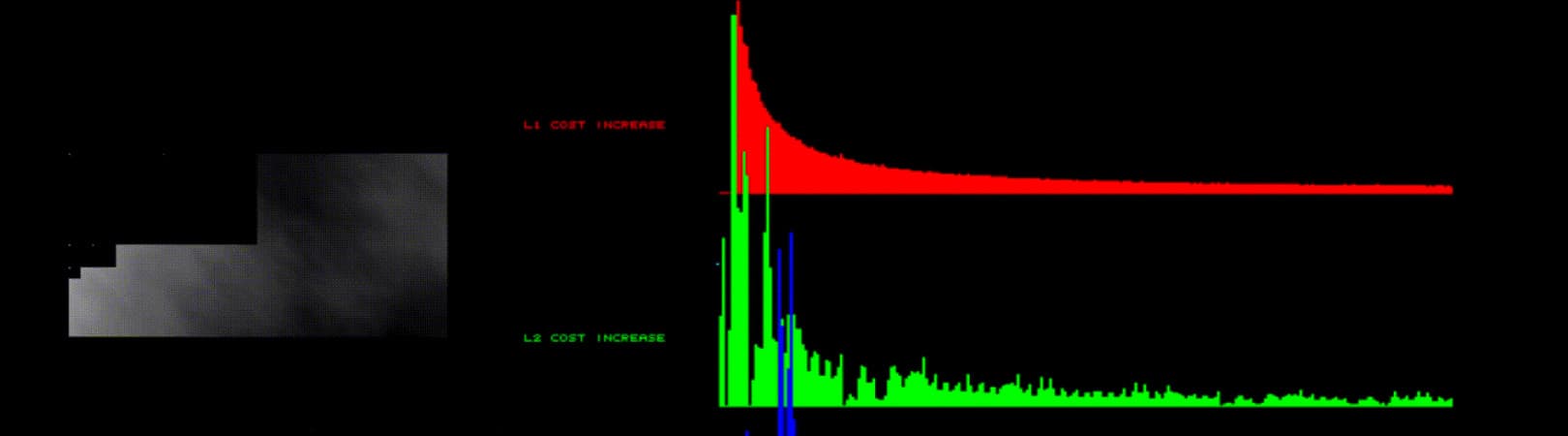

Real-Time L1-L2-L3 Cache Behavior

Features & Performance

The simulator supports read and write operations for multiple data types, including short, int, and long (16- and 32-bit values). It implements five eviction policies: Random (R), Round Robin (RR), Least Recently Used (LRU), Most Recently Used (MRU), and Least Frequently Used (LFU). Real-time interactive visualizations display hit/miss behavior and cost increase over time for each cache level. Using a 32-way set associative cache with the Round Robin policy, the system achieved approximately a 95% efficiency improvement compared to the Fully Associative cache configuration.